#### Electronics and Communication Engineering Department

Total marks: 20marks

Ministry of Higher Education High Institute of Engineering & Technology In New Damietta

Date: 28 /7/2018

Subject: integrated circuits Subject code:

No. of questions: 3 No. pages: 2 Time: 11:00 - 12:30 pm (1.5h)

Mid Term Examination, summer Semester 2017-2018- Dr. Amira Elsonbaty

1: What is an IC& Why are ICs more reliable than discrete circuits? ). [2 marks]

ICs are more reliable because of elimination of soldered joints and need for fewer interconnections.

2: Write short notes about IC structure & its Classification (technology, Type, Size). [1 marks]

An integrated circuit (IC) is one in which all active and passive components such as transistor, diodes; resistors, capacitors etc. are automatically part of a small semiconductor chip. ICs are more reliable because of elimination of soldered joints and need for fewer interconnections.

IC Classification

☐ Circuit technology (BJT, BiCMOS, NMOS, CMOS)

☐ Design style (Standard cell, Gate Array, Full Custom, FPGA)

☐ Design Type (Analog, Digital, or Mixed-Signal)

☐ Circuit Size (SSI, MSI, LSI, VLSI, ULSI, GSI)

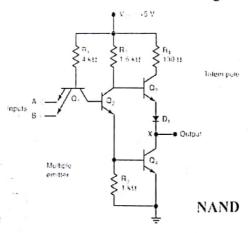

3: What is the basic function of TTL gate?1 MARK

The basic function of TTL gate is NAND function. It is the most popular logic family.

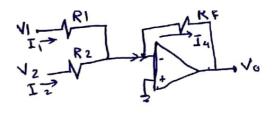

**4**: <u>How many</u> op-amps are required to implement this equation VO = V1? <u>Explain</u>? [2marks]

One op-amp

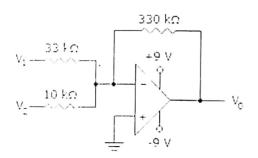

5: Calculate the output voltage if V1 = -0.2 V and V2 = 0 V.[4marks]

$$V_0 = -R_f \left( \frac{VI}{R_1} + \frac{V_2}{R_2} \right)$$

= -330 \left( \frac{-0.2}{33} + \frac{6}{10} \right)

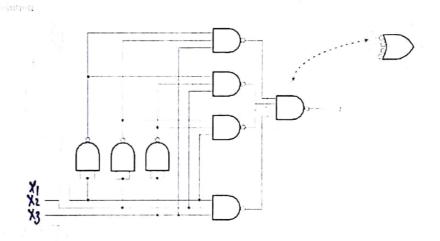

# 3: Analysis and Design the Digital Integrated Circuit

Design Procedure

- 1. Specification

- Write a specification for the circuit if one is not already available

### 2. Formulation

Derive a truth table or initial Boolean equations that define the required relationships between the inputs and outputs, if not in the specification Answer: Option A

- 7: Transistor-transistor logic (TTL) is a class of digital circuits built from

- a) Transistors only

- b) Bipolar junction transistors (BJT)

- c) Resistors

- d) Bipolar junction transistors (BJT) and resistors

Answer: d

- 8: In DTL logic gating function is performed by

- a) Diode

- b) Transistor

- c) Register

- d) Capacitor

Answer: a

- 9: In DTL logic gating function is performed by

- a) Diode

- b) Transistor

- c) Register

- d) Capacitor

Answer: a

- 10. To increase fan-out of the gate in DTL

- a) An additional capacitor may be used

- b) An additional resister may be used

- c) An additional transistor and diode may be used

- d) None of the Mentioned

Answer: c

Explanation: To increase fan-out of the gate in DTL, an additional transistor and diode may be used. Here, the fan out means the number of maximum output.

| Question (2): Choose the correct answer for the following                         | [5 marks]             |

|-----------------------------------------------------------------------------------|-----------------------|

| 1: In a TTL circuit, if an excessive number of load gate inputs are connected,    | ·                     |

| A. V <sub>OH(min)</sub> drops below V <sub>OH</sub>                               |                       |

| B. V <sub>OH</sub> drops below V <sub>OH(min)</sub>                               |                       |

| C.V <sub>OH</sub> exceeds V <sub>OH(min)</sub>                                    |                       |

| D.V <sub>OH</sub> and V <sub>OH(min)</sub> are unaffected                         |                       |

| Answer: Option B                                                                  |                       |

| 2: The greater the propagation delay, the                                         |                       |

| A.lower the maximum frequency                                                     |                       |

| B. higher the maximum frequency                                                   |                       |

| C.maximum frequency is unaffected                                                 |                       |

| <u>D.</u> minimum frequency is unaffected                                         |                       |

| Answer: Option A                                                                  |                       |

| 3: Which equation is correct?                                                     |                       |

| $\underline{A}.V_{NL} = V_{IL(max)} + V_{OL(max)}$                                |                       |

| $\underline{B}.V_{NH} = V_{OH(min)} + V_{IH(min)}$                                |                       |

| $\underline{C}.V_{NL} = V_{OH(min)} - V_{IH(min)}$                                |                       |

| $D.V_{NH} = V_{OH(min)} - V_{IH(min)}$                                            |                       |

| Answer: Option D                                                                  |                       |

| 4: ECL IC technology is faster than TTL technology.                               |                       |

| A.True                                                                            |                       |

| B.False                                                                           |                       |

| Answer: Option A                                                                  |                       |

| 5: CMOS is a more dominant IC technology than TTL.                                |                       |

| <u>A.</u> True                                                                    |                       |

| B.False                                                                           |                       |

| Answer: Option A                                                                  |                       |

| 6: The greater the propagation delay, the higher the maximum frequency.           |                       |

| A.True                                                                            |                       |

| B.False                                                                           |                       |

| Answer: Option B                                                                  |                       |

| 6: There are four different logic level ranges for TTL and CMOS: VIL, VIH, VOL, a | ind V <sub>OH</sub> . |

| <u>A.</u> True                                                                    |                       |

| B.False                                                                           |                       |

## 3. Optimization

- Apply 2-level and multiple-level optimization

- Draw a logic diagram or provide a netlist for the resulting circuit using ANDs, ORs, and inverters

## 4. Technology Mapping

- Map the logic diagram or netlist to the implementation technology selected

### 5. Verification

- Verify the correctness of the final design